Microprocessor-based VPX platforms enable advanced signal processing

StoryJanuary 17, 2014

Improved power-to-performance ratios with multicore processors in VPX systems are boosting viability and reducing reliance on the high costs of FPGA development. Since they fundamentally change the way signal processing is implemented, parallel-rate microprocessors do away with hand-coding threads and math algorithms and more efficiently bring together powerful computing platforms that can take full advantage of state-of-the-art processor features. (Lead image: U.S. Army Spc. Nathan Williams from the 263rd Army Air Missile Defense Command deploys a Sentinel radar system. Radar systems like Sentinel depend on high-performance signal processing systems. DoD photo by Staff Sgt. Jacob N. Bailey, U.S. Air Force.)

Until recently, general-processor architectures lacked the mathematical algorithms to keep up with DSPs and GPUs in terms of megaflop parallel processing. In addition, the reccurring costs of designing signal-processing systems that utilize FPGAs, such as software-defined radio, became quite expensive. In the processor-architecture world, advancement of smaller and faster processors is running up against physical limitations, but Moore’s Law is kept alive and well by utilizing multicore processors.

Today, the trend for military signal processing-based applications is to migrate to VPX platforms based on multicore processors that have built-in multithreading capabilities and are backward-compatible with older processor technology. Based on Intel’s proven commitment to bring forward the technologies of old generations onto newer chipsets, the complete redevelopment of software is not required with each new chip release

Coupled with advances in microprocessors, designers are also gaining I/O performance advantages from combining VPX and Generation 3 Peripheral Component Interconnect Express (PCIe 3.0). This more-powerful option enables the equivalent of exchanging one DVD of data every second between boards, thereby evolving military design well beyond the parallel bus architectures that in the past seriously limited I/O performance. Applications are delivering on the promise of significant performance improvements in small-form-factor systems, which suit rugged, mobile deployment. Overall, systems using mainstream technologies such as TCP/IP, PCI Express (PCIe) and Intel CPUs have a well-defined opportunity to transform the military into a network-centric force, driven by high-level performance.

The value of VPX

Networking the soldier continues to be a primary goal, particularly in the face of fiscal challenges and the resulting changes in procurement policies. To reel in costs even further, the DoD has started to implement an “agile acquisition process” that mandates proof-of-concept (PoC) prototypes, which requires developers to innovate systems faster in a more competitive environment.

Designs submitted under this process must be more rugged to accommodate broad deployment in a variety of environments, with more sensors processing a greater amount of information in real time. CPU and I/O performance must match in order to take advantage of sensor data and eliminate any potential data-processing bottlenecks.

Microprocessor-based VPX platforms answer these needs, offering parallel processing with ideal power-to-performance ratios, including mainstream technology such as PCIe Gen 3 and TCP/IP. These options avoid the need for specialized code and development resources dedicated to FPGAs and keep developers designing in step with agile acquisition challenges, minimizing the costs of delivering PoC prototypes to win DoD contracts.

Power-to-performance advances fuel DSP apps

While DSP chips and FPGAs were often the primary design choice for executing heavy digital signal processing (DSP) functions, these options often complicated designs in terms of programming and power consumption. Where FPGAs were once required to get past the power barriers and were needed to handle massive parallel processing, Intel processors are now used in DSP scenarios such as radar, sonar, surveillance reconnaissance, and unmanned aerial and ground platforms.

Intel’s Advanced Vector Extensions (AVX) enables a microprocessor alternative to DSP and FPGAs; AVX is integrated into its multicore platforms and doubles the processor’s vector engine capability from 128 to 256 bits. This upgrade creates a dramatic improvement in floating-point-processing capabilities, which is ideal for sophisticated signal-processing designs. Designers have the distinct advantage of developing high-performance GFLOPS processing applications, but in the familiar territory of the general-purpose processor.

Current Intel processors also integrate Intel Hyper-Threading Technology, which boosts performance by enabling a single core to perform as two virtual cores. Intel Primitive Processing (Intel IPP) further enables the floating point unit to do matrix algebra – optimizing DSP algorithm implementation – and with each generation of Intel processor comes a considerable increase in floating-point performance.

The new Intel-based High Performance Embedded Computing (HPEC) VPX systems offer the processing power of a supercomputer in a small 3U form factor, which can handle radar computative processing (that is, space, time, and adaptive applications) in real time at longer range. Detectability is remarkably improved, with no lag time or waiting for results. Imagery is also available in real time, compared to previous generations of intelligence gathering, where soldiers had to wait between 2-24 hours for the same information. Faster data-gathering this enables a powerful new era of situational and offensive awareness. Since the algorithm is more efficiently handled with these new platforms, resolution between target, noise, and interferer is improved dramatically, harnessing processing power that decreases the granularity of detection even in noisy environments.

Optimized compilers simplify VPX development

Just as the hardware has changed over time, there have been significant software updates as well. Today, for example, six cards that have two quad-core processors each allow developers to more efficiently distribute the load across the system and let the software utilize the multithread environment. Direct memory access is achieved to other boards via the backplane in modern software-defined radio/RF, navigation systems, and mission-progress applications, with reduced size, weight, and power (SWaP).

Systems have migrated from restrictive proprietary OS options and communication software to open standards such as Linux and TCP/IP. Overall, technology has helped push the limits of new software paradigms that can readily ease development of complex systems. For example, 4th-generation compilers have been specifically designed to automate specific portions of military applications, freeing the software developer from having to learn new hardware configurations to maximize performance on today’s modern architectures. By meeting the time and budget constraints of the competitive military- acquisition environment, standardized VPX platforms and related software tools have become timely resources for rapid demo and prototype system development.

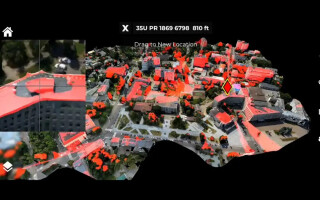

Through automation of the dataflow design, sophisticated compilers handle many of the manual coding, debugging, and fine-tuning requirements of application software. Illustrated by Kontron’s StarVX VPX platform (Figure 1) integrated with Gedae’s Idea parallel compiler, application design and development time is reduced by as much as half, through automation of parallel sensor development and deployment software. By compiling for the complete StarVX system instead of for just a single processor, Gedae’s compiler offers a resource that reduces prototyping investments and uses the compiler to develop the rest of the application. No design effort is wasted in the process.

Figure 1: Kontron’s StarVX is a prequalified Proof of Concept platform for military/aerospace system developers. StarVX includes open standards technologies such as VPX, Ethernet, Intel processors, Linux, and software compiler tools that are either integrated into StarVX or support it. StarVX runs on Linux, reducing development time and allowing for growth and portability to save initial software expenditure.

(Click graphic to zoom by 1.9x)

Integrating VPX with PCIe Gen3

OEMs are also facing the challenge to select a simple – albeit fast – low-latency communications protocol, ideal for applications such as image-intensive targeting and surveillance, real-time video processing for situational awareness, next generation radar or sonar, or 3-D mission simulation for field training. With the VPX and PCIe 3.0 architecture, rugged high-performance applications can perform well in a small space while avoiding being locked into proprietary technologies. Software investments are protected over time, and TCP/IP applications can operate unchanged on proven, ruggedized VPX platforms. High-Performance Embedded Computing (HPEC) PoC systems are validating these performance characteristics, delivering as much as ten times the I/O data bandwidth previously achieved in computing platforms for military systems.

Low-overhead, low-latency data transfers are enabled by PCIe 3.0, linking high bandwidth I/Os to a processor unit and operating as a native communication link between computing devices in a multiprocessor environment. Scalable, simultaneous, bidirectional transfers use from one to 32 lanes of differential-pair interconnects. Similar to graphics adapters, lanes are grouped to achieve high transfer rates, with as fast as 32 GB per second of bidirectional bandwidth possible on an x16 connector. Using both host-directed and peer-to-peer transfers, emulation of network environments can send data between two points without host-chip routing.

VPX PoC systems readily tap into high-speed PCIe 3.0 bandwidth for data transfers by selecting a different IP address to connect to the other boards. Software coding is unaffected, and applications are shielded from the low-level yet complex details of the current generation of PCIe silicon management. PCIe’s performance as a native data bus in all modern processor chipsets further establishes tangible military design value in the form of a broad PCIe-based software ecosystem with well-developed support for peripheral interconnects.

Prevalidated systems accelerate development of signal processing apps

Prevalidated platforms such as StarVX enable ease of development, as designers already have extensive experience in working with all of technology used by the system. Integrated generic IT technology such as x86, Linux, TCP/IP, and PCIe eliminate niche-based deployments and reduce the risk of obsolescence. With massive I/O bandwidth and IP sockets available, designers can complete their PoC on mainstream IT servers and deliver the system unmodified.

By combining microprocessor-based VPX systems with PCIe 3.0, developers are accessing an entirely new and unparalleled class of signal-processing applications with high-speed data processing in harsh environments. Multi-gigahertz signals give VPX connectors and backplanes the capability of one or more dedicated 10-Gb connections via Ethernet or PCIe, and the full dataplane bandwidth is no longer shared between boards. Kontron’s VXFabric software (Figure 2) links this technology to currently deployed applications that exchange data via gigabit Ethernet, providing point-to-point protocol transfer and greater than 10-Gb speeds without the need for a switch.

Figure 2: VXFabric software reduces development costs by simplifying and speeding application development of inter-CPU communications in VPX system architectures while also enabling migration to emerging hardware communication solutions in the embedded domain, such as 10G and 40G Ethernet.

VXFabric, the physical layer used by the TCP/IP socket API, implements the TCP/IP protocol over the PCIe infrastructure; this arrangement boosts transmission bandwidth to greater than 10 GbE speeds and delivers up to 4.2 GB/s in data throughput between VPX boards in a rack. Further optimizing the switch fabric, this PoC platform uses TCP/IP on top of PCIe and in addition to Ethernet as the system dataplane.

Mainstream tech gives VPX a competitive edge

VPX systems that employ multicore processors provide an ideal signal-processing solution – not only because of power-to-performance improvements, multithreading capabilities, and backwards compatibility with older processors – but also because of simplified development using mainstream technologies. FPGAs or microprocessors each have their roles in specific signal-processing applications, but current processor advancements have made multicore systems more viable than ever. At the same time, Network Integration Evaluation (NIE), part of the military’s “agile acquisition process,” mandates that resources shift away from research, development, test, and evaluation (RDT&E), and focus instead on the procurement of mature network capability that can be quickly deployed.

POC microprocessor-based VPX systems are deployable quickly and capitalize on mainstream technologies such as TCP/IP and PCIe. These proven systems reduce development time and cost in the quest to provide massive processing power for compute-intensive systems, while integrating high-performance COTS technologies to meet immense throughput and processing requirements.

RJ McLaren is Portfolio Manager, Commercial Avionics & Military Products at Kontron.

Glenn Johnson is Systems Architect, Commercial Avionics & Military Products at Kontron.